procesoare micro-arhitectură

Acasă »Componente PC» microarhitecturii CPU

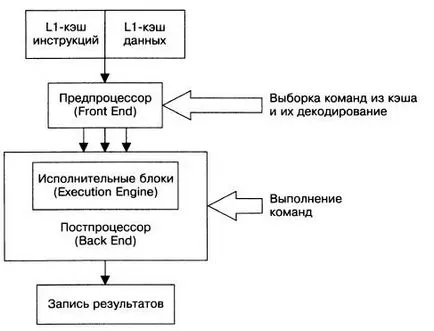

Înainte de a trece la luarea în considerare a arhitecturi de procesoare reale, opțional-go aminti principiile de procesoare pe baza unei scheme structurale simplu a ipotetic sau procesor „clasic“. În orice arhitectură bazată pe procesor este mai multe elemente constructive: un cache de instrucțiuni și un preprocesor de date (Front End) și un post-procesor, numit, de asemenea, o unitate de execuție instrucțiune (Motor de executie).

Datele de proces constau din mai multe etape tipice. Mai întâi de toate instrucțiunile și datele sunt preluate din cache L1 (care este împărțit în cache în cache și date tru). Această procedură se numește probă. Apoi, va jur-cache instrucțiuni sunt decodificate în înțeles pentru un anumit primitivelor procesor (mașină de instrucțiuni). Aceasta se numește decodare. În continuare, instrucțiunile decodificate furnizate unităților de procesor executive sunt realizate, iar rezultatul este scris în memorie.

eșantionare procesează instrucțiuni din memoria cache, decodificarea și promovarea lor în plus blocuri este realizată în-preprocesor și executarea procesului a instrucțiunii decodificat - în Postprocessor. Astfel, chiar și în cazul cel mai simplu al unei pro-comandă are loc cel puțin patru etape de prelucrare:

1. Eșantionul a memoriei cache;

4. Înregistrați rezultatele.

Aceste etape sunt numite comenzi de procesare de conducte. În cazul nostru, este o conducta de patru etape. Este important ca fiecare dintre aceste etape echipa ar trebui să aibă loc exact un ciclu de ceas. În consecință, pentru patru sute-transportor-etapă pentru a efectua o singură comandă este dat exact patru accidente vasculare cerebrale.

aspect structurale ale Înlănțuire procesor „clasic“

Desigur, am considerat procesor este într-o anumită măsură, ipotetic-CAL. În procesoare reale instructiune de procesare de conducte pot fi mai complexe și includ mai multe etape. Cu toate acestea, structura însăși a ideologiei procesorului rămâne neschimbată. Motivul pentru creșterea lungimii transportorului este că o mulțime de echipe sunt destul de complexe și nu se poate face într-un singur ciclu de ceas, mai ales la frecvențe înalte. Prin urmare, fiecare dintre cele patru etape de prelucrare de instrucțiuni (fetch, decodifica, executa, scriere) poate consta din mai multe etape de conducte. Corectă, dar lungimea transportorului este una dintre cele mai importante caracteristici ale oricărui CPU.

În cazul procesului de prelevare a probelor „clasic“ ipotetic proces de executie procesor set-cod începe cu instrucțiuni și date din cache L1. Cu toate acestea, în scopul de a instruire și cache-ul de date a lovit în acest sens, au nevoie pentru a preîncărca conținutul memoriei. Acest proces se numește date prefetch și instrucțiuni din memoria principală.

În conformitate cu schema de „clasice“ procesor execută procedura de procesor de cod începe cu instrucțiuni de eșantionare în format x86 și datele din memoria cache L1. instructiuni x86 sunt de lungime variabilă, iar lungimea informațiilor de instrucțiuni sunt stocate în câmpurile speciale în instrucțiunile cache L1. Încărcarea instrucțiuni de lungime variabilă x 86 are loc L1 blocuri cache de o anumită lungime, din care mai multe instrucțiuni distincte care suferă de decodare.

Atunci când a întâlnit în ramura fluxul de instrucțiuni sau tranziții, prelevarea de probe din blocul de instrucțiuni coada-TION este produsă cu ajutorul mecanismului de ramură de predicție.

Fiecare procesor trebuie să fie în cele din urmă construite în așa fel încât timpul minim pentru a efectua numărul maxim de instrucțiuni. Acesta este numărul de instrucțiuni executate pe unitatea de timp și determină performanța procesorului.

Există două abordări fundamental diferite de îmbunătățire a procesorului producător-Ness (nu de numărare, desigur, crește frecvența de ceas). Sunt primele doua este faptul că prin reducerea lungimii transportorului pentru a crește numărul de unități de execuție. Astfel, puse în aplicare în mod substanțial pluralitate de benzi transportoare paralele scurte. În acest caz, Postprocessor funcționează prin sistemul clasic: preia comenzi, le decodifice și Trimite-bau pe mai multe unități de execuție. O astfel de abordare permite realizarea pe deplin paralelismul la nivel de instruire (Instruction-Level paralelism, ILP), atunci când mai multe instrucțiuni sunt executate simultan în diferite blocuri executive-ing procesor. Este important ca numărul de etape de conducte din postprocesor (unitatea de acționare) este mic, astfel încât declarațiile sunt executate pentru un număr mic de cicluri.

Pentru a pune în aplicare paralelismul la nivel de instrucțiuni impune ca post-Payuschie la unitățile de execuție ar putea executa comenzi în paralel. Cu toate acestea, în cazul în care, de exemplu, pentru a efectua următoarele instrucțiuni în ordine Tre Buet cunosc rezultatul anterior (instrucțiunile de instruire interdependente), în acest caz, executarea în paralel nu este posibilă. Prin urmare, preprocesorul verifică mai întâi interdependenta echipe și Reordonare Chiva-ele nu sunt în ordinea primirii (de ordine), și, astfel încât acestea să poată fi executate în paralel. În ultima etapă a instrucțiunilor de conducte rds-ivayutsya în ordinea inițială.

conducte scurt, după cum, într-adevăr, și un lung, are propriile sale forte și punctele slabe, Stora-ne. Cu cât numărul de etape în care transportorul este împărțit, cantitatea minimă de muncă se efectuează în fiecare etapă și, prin urmare, este necesar mai puțin timp pentru finalizarea acestei comenzi etape. Având în vedere faptul că fiecare etapă este realizată într-un singur ciclu de instrucțiuni, benzi transportoare lungi permit să crească frecvența de ceas a procesorului, ceea ce este imposibil în cazul transportoarelor co-subscurta.

Cu o scurtă conductă în fiecare etapă a procesorului se poate ocupa de durere, cantitatea de gât de muncă, dar pentru a trece instrucțiuni prin fiecare etapă a conductei este nevoie de mai mult timp, ceea ce limitează creșterea vitezei procesorului. În acest caz, creșterea numărului de instrucțiuni executate pe unitatea de timp, se realizează prin paralelizare instruire și unități de procesor executiv tencuite-vanija.