În două etape T-flip-flop - studopediya

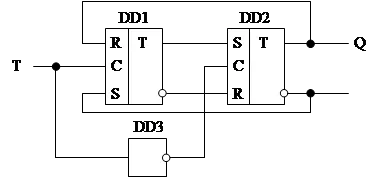

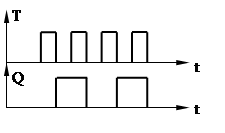

În declanșare în două etape care cuprinde două serii a inclus dispozitivul de blocare cu feedback-uri, „noi“ informații sunt stocate în primul flip-flop menținând în același timp informațiile „vechi“ în al doilea. Când este stocat „noi“ informații, și un semnal activ este îndepărtat de intrare TS șterge informațiile „vechi“ și a adăugirilor „noi“ informații pentru al doilea declanșator. Schema două trepte T-flip-flop, construit pe două RS-bistabile sincrone și graficul său de sincronizare funcționare prezentat în Fig. 5.9.

Fig. 5.9. Schema (a) și diagrama de temporizare a (b) două etape T-flip-flop

A doua trepte T flip-flop este format din două bistabile - master și slave DD1 DD2. Pentru a elimina intrările de generare de ceas modul de circuit de bistabilelor incluse prin invertor DD3, adică sincronizarea se obține nivele logice răsturnate. Feedback-uri cu acces direct la intrarea DD2 R DD1 și DD2 de ieșire S inversat DD1 pentru a crea semnale de intrare funcționează algoritmul de potrivire T-flip-flop. Rețineți că ieșirea din două trepte T-bistabilului apare după îndepărtarea unui semnal de intrare T activ atunci când informația este suprascrisă din primul bistabilul în al doilea. Acest lucru asigură funcționarea normală (fără generare de impulsuri) în circuit cu feedback-ul.

Pentru a distinge de declanșare în două etape printr-o singură etapă, sa imagine grafică condiționată plasată scrisoare dublă (TT).

5.6. Cele două etape JK simultane -trigger

O trăsătură distinctivă a JK -triggera este că nu a interzis combinații de semnale de intrare la intrarea de informații. JK -triggera lucrare descrie tabelul de tranziție (Tabelul 5.5), în care semnalul activ este considerat logic 1. activ de intrare J semnal de declanșare comută la Q starea = 1, iar intrarea K - la Q = 0.

Tabelul tranzițiilor JK -triggera

Fig. 5.10. Schema bloc JK -triggera

După cum se poate observa din diagrama, intrările elementelor 3I DD3 sau DD4 DD2 furnizate cu ieșirea de declanșare a semnalului și o unitate logică 0 logic. De aceea, intrările J și K pot fi orice semnale, dar în S și intrările R DD1 simultan două semnal activ nu poate ajunge.

JK -trigger este universală. Pe această bază, puteți crea orice fel de circuit flip-flop. Fig. 5.11 arată punerea în aplicare a tuturor considerate anterior JK flip-flops -triggere.

Fig. 5.11. Punerea în aplicare a declanșatoare bazate pe JK -triggera:

și - sincron RS-FF; b - D-flip-flop; în - T-bistabilul

Într-o serie de TTL JK -trigger făcut pe K155TV1 cip, seria CMOS - K561TV1 și K176TV1, care este tot pe un singur cip din serie. Acest lucru se datorează cererii reduse pentru flip-flops cu control static pentru a fi utilizate în sistemele de automatizare și control de la distanță.