Elementele de bază ale tehnologiei digital cu microprocesor

dispozitiv de memorie semiconductor

4.1 Elemente de tehnologie microprocesor

Integral declanșatoare declanșatoare sunt de obicei puse în aplicare pe NAND logic, NOR. Declansatorul este proiectat pentru a stoca valoarea unei variabile logice (sau valoarea numărului de un bit binar, un declanșator separat utilizat când stocarea numerelor binare multi-bit pentru stocarea valorilor fiecărei descărcării). În conformitate cu aceasta, declanșatorul are două stări: una dintre ele este menționată ca un stat 0, celălalt - ca o stare de 1. Atunci când se lucrează la intrările de declanșare, este setat la starea dorită.

Declanșatorul are două ieșiri: directă Q-lea și inversiuni. Condiția în care declanșatorul este determinat de nivelul de tensiune la aceste ieșiri, dacă tensiunea la ieșirea Q-Corespunzător există un nivel logic 0 (Q = 0), se presupune că bistabilul este în starea 0, Q = 1 atunci când declanșatorul este 1. starea de nivel logic la inversul vyhodepredstavlyaet o inversare TION cuprinzând un declanșator (la 0 = 1, și vice-versa).

Declanșările sunt diferite tipuri de intrări. Denumirile și numirile lor:

R (. Din Reset English) -razdelny setat de intrare la starea 0;

S (. Din setul de limba engleză) -razdelny setat de intrare la starea 1;

K universal dispozitivul de blocare set de intrare în starea 0;

J - dispozitivul de blocare setat de intrare universală în starea 1;

D (de la Delay limba engleză.) - flip-flop set de informații de intrare la starea corespunzătoare nivelului logic pe această intrare,

C-control (ceas) de intrare.

Numele de declanșare determinat de tipurile de intrări sale. De exemplu mer, RS-trigger - flop având intrări R și tip S.

Prin natura reacției pentru a declanșa semnale de intrare sunt împărțite în două tipuri: sincrone și asincrone. In trăgaciul asincron semnalele de intrare afectează starea de flip-flop direct la momen-ta-i hrănească la intrările, în declanșatoare sincron - numai atunci când se aplică un semnal de ceas la intrare de control C.

declanșatoare asincrone

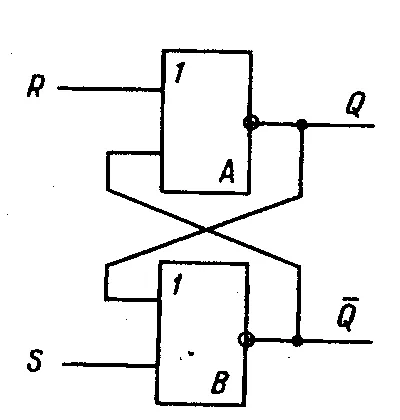

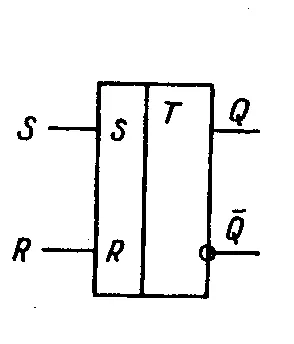

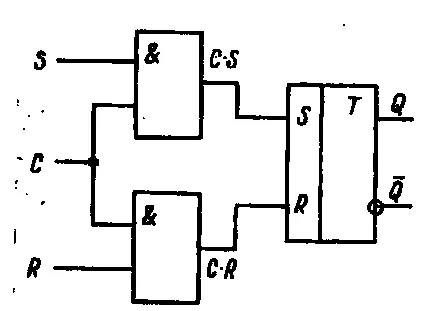

RS-declanșare cu intrările directe. Structura logică a pre-declanșare prezentat în Fig. 4.1a. Declanșatorul este construit pe două și elemente logice conectate astfel încât ieșirea fiecărui element al sub-cheie pentru cealaltă a intrărilor. Astfel de elemente de legătură ale dispozitivului oferă două stări stabile. Comutarea zăvorului de la o stare stabilă la alta are loc atunci când se aplică semnalele active de pe intrările.

Fig. 4.2b arată valoarea condiționată a aproximativ asincron RS-flip-flop.

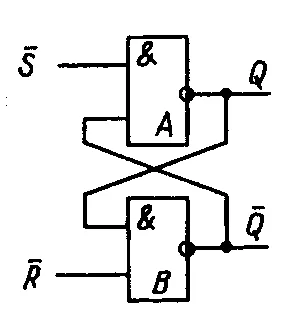

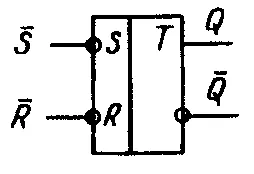

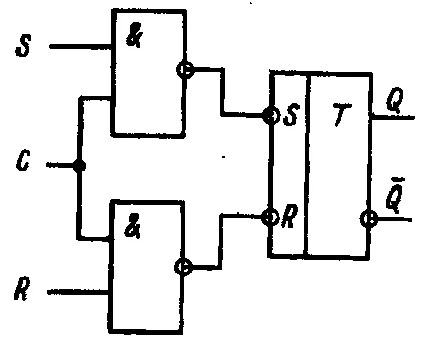

RS-declanșare cu intrări inversate

Structura logică a bistabilului prezentat în Fig. 4.1, de asemenea. Spre deosebire de structura logică a RS-zăvor cu liniile de intrare discutate mai sus este doar faptul că elementele logice utilizat aici politisti-AND-NO. Fig. 4.2b arată simbolul RS-FF intrări-inversiune guvernamentale.

Sincronă bistabile cu control static

Spre deosebire de declanșare asincron sincron este faptul că declanșatorul sincron are o intrare suplimentară numită sincronizare (această intrare este adesea menționată ca intrări de sincronizare). Numirea de intrare de ceas pentru acest semnal de intrare pentru a permite recepția semnalelor de la intrările de date (semnale care intrările de comutare de declanșare se efectuează) la intervale de timp predeterminate. În absența unui semnal sincron intrări de date de intrare-ziruyuschem dezactivat în mod logic și semnalele de pe aceste intrări nu afectează starea de flip-flop.

Virtutea declanșatori sincrone este că acestea sunt permite pentru a elimina efectul diferențelor în valoarea de întârziere în semnal-nenii elemente de circuit separat Prevalența. Aceasta asigură recepția simultană a semnalelor în diferite părți ale circuitului la intervale de timp predeterminate.

declanșatoare sincrone, la rândul lor, sunt împărțite în două tipuri: sincrone flip-flops cu control static și declanșează sincron cu control dinamic. Primele declanșatori reacționează la schimbările datelor de intrare de semnal de informații care apar în timpul acțiunii pe intrarea de semnal de sincronizare. Prin urmare, aceste schimbări sunt doar semnal de toleranță-absență la intrarea de sincronizare. In declanșatoare sincronizate cu semnalele de control dinamic de la intrările de informații de recepție are loc în timpul muchia scurtă durată a semnalului (pozitiv sau negativ) este sincronizat cu intrarea de-al. Restul intrărilor de date sunt deconectate în mod logic, și a permis semnalelor schimba pe intrările infor-mațiile și pe durata semnalului de ceas (excluzând lungimea partea frontală).

RS-flip-flop. Fig. 4.3a, b prezintă structura logică a sincronizator TION RS-declanșare. După cum se vede din aceste structuri, un sincron RS-declanșare include asincron de declanșare directă (sau invers) WMOs rândurilor R intrărilor și S din care include porți ȘI (AND-NO).

Folosind porți ȘI (AND-NO) asigură transmiterea nivelurilor logice ale intrărilor informaționale active ale S și R ale sincron flip-flop la intrările S și R fiind un declanșator asincron-parte picior numai când nivelul jurnalului. 1, la intrarea de ceas C.

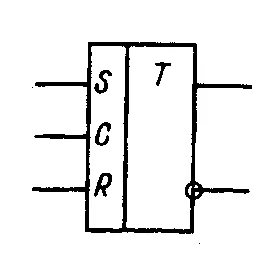

Fig. 4.3 arată simbolul sincron RS-FF.

D-flip-flop. Acest tip de flip-flop are doar o intrare de date D. Conectare C - control, și servește pentru a sincroniza semnal de alimentare prezent.

declanșatoare sincrone, construit pe principiul stocării informațiilor în două etape

Caracteristică declanșează un memorizarea două etape de informare TION este faptul că acestea conțin două moduri de declanșare: unul este un declanșator lider așa-numita, celălalt - sclavi flip-flop. Atât funcția de declanșare ca un sincron bistabilelor cu control static.

Când ceasul de intrare c = 1, declanșatorul principal este setat la starea corespunzătoare semnalelor de intrare de la intrarea de informații. Slave flip-flop au inversat o intrare de ceas, astfel imun la informațiile primite de la intrare de la ieșirea din dispozitivul de blocare de master. El continuă să fie într-o stare care a fost instalat (în ciclul de ceas precedent).

Atunci când valoarea C (C = 1 C = 0) este deconectat de la intrările de date flip-flop de master și încetează să răspundă la modificările valorilor semnalului de la aceste intrări; slave flip-flop este setat la o stare în care trăgaciul lider. Din acest punct de valoarea setată de intrare corespunzătoare semnalelor de intrare primite de momentul în care a considerat momentul de margine de semnal la intrare.

controlul proceselor în trăgaciul cu informații-dvuhstupencha lea pentru zăvorâre perioada de ceas osuschest-S cele două fronturi ale semnalului pe intrarea de ceas: o margine pozitivă apare la lider setarea declanșare pe o muchie negativă - zăvorul slave.